芯片工艺突破0.2nm,2046年仍有增长空间

行业观察:芯片工艺极限远未到来,IMEC勾勒0.2nm以下未来蓝图

尽管“摩尔定律已死”的论调甚嚣尘上,但业界对芯片制造工艺的物理极限似乎仍持谨慎乐观态度。比利时欧洲微电子中心(IMEC)近期发布的最新工艺路线图,不仅驳斥了近期内工艺停滞的悲观预测,更描绘了芯片制造技术在未来二十余年内持续演进的宏伟蓝图。该路线图预示,到2046年,芯片制造工艺有望突破0.2nm的界限,继续向更微小的尺寸迈进。

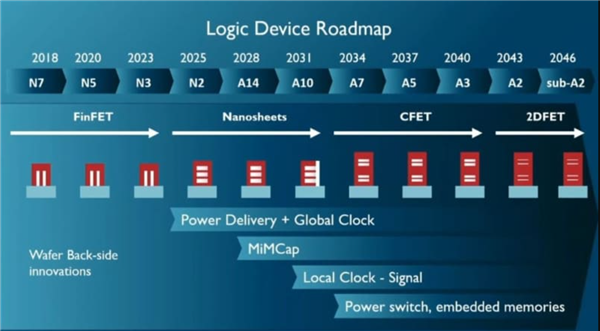

IMEC的路线图显示,从2018年的7nm N7工艺,到3nm N3工艺,FinFET晶体管技术一直是推动芯片制造的关键。去年发布的2nm N2工艺开始引入GAA(Gate-All-Around)晶体管结构,并采用NanoSheets技术,预计这一技术路线将持续支撑至2031年,实现1.4nm级别的A14工艺和1.0nm级别的A10工艺。此后,到2034年,0.7nm级别的A7工艺将登场,届时,GAA晶体管结构将面临瓶颈,取而代之的是全新的CFET(Complementary FET)晶体管结构。

CFET结构的核心在于将N型和P型晶体管垂直堆叠,理论上可实现近乎一半的面积缩小,从而显著提升芯片集成度。然而,这种垂直堆叠的设计也带来了巨大的散热挑战,成为其大规模量产前的关键技术难点。CFET结构预计将一直服务于芯片工艺发展直至2040年的0.3nm A3工艺。在此之后,芯片制造将进入一个全新的阶段,可能采用传闻已久的2D FET(二维晶体管)技术,标志着芯片工艺进入二维材料时代。2D FET以其原子级的精确厚度,被视为实现超微缩芯片工艺的终极解决方案,尽管目前包括台积电、三星和Intel在内的多家巨头已展示相关技术,但距离实际量产仍有待时日。

芯片工艺演进的挑战与机遇

2D FET结构的引入,有望驱动芯片工艺一路狂奔至Sub-A2级别,即0.2nm以下,按照目前的命名惯例,可能达到0.14nm。尽管这一目标尚需二十年时间,且过程中每一步的工艺提升都将极为艰难,但IMEC的路线图为芯片行业的发展指明了方向。值得注意的是,在2nm节点之后,芯片面积的微缩已不再是主要看点,工艺节点命名也变得更加复杂,例如A13、A12等工艺的出现,正是在填补现有技术代际间的空白,以应对提升密度愈发困难的局面。

除了核心的晶体管结构演进,芯片工艺的整体突破还依赖于散热、供电及先进封装等多个维度的技术创新。谁能在这些关键领域率先取得突破,谁就有可能在未来二十年的工艺竞赛中脱颖而出,甚至超越当前的行业巨头。同时,我们也期待中芯国际、华虹、晶合集成、芯联集成等中国大陆的半导体企业,能够抓住这一历史机遇,从追赶者转变为引领者,深度参与到全球芯片工艺的下一轮竞争中。

IMEC的未来工艺路线图,为打破“摩尔定律已死”的论调提供了坚实的技术基础,同时也预示着芯片制造领域将进入一个充满挑战与机遇的新时代。能否克服结构性难题,并在散热、供电、封装等配套技术上实现突破,将是决定未来芯片性能与成本的关键。