AI十二小时设计出完整CPU,缩短研发周期

AI自主设计CPU核:Verkor.io的行业新探索

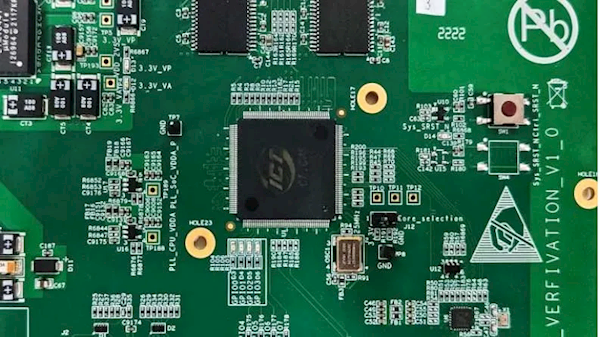

近期,AI芯片设计初创企业Verkor.io公布了一项在AI辅助芯片设计领域的潜在突破。该公司在3月发布的研究论文中,详细介绍了其名为DesignConductor的智能AI系统,能够仅凭一份219字的需求文档,在12小时内自主完成一款完整RISC-V架构CPU核的全流程设计,并输出可直接用于版图流片的GDSII文件。

这一成果若能进一步成熟,将可能对传统的芯片设计周期产生颠覆性影响。目前,商业芯片设计行业普遍需要18至36个月才能完成一款CPU核的设计。Verkor方面表示,这是行业内首次由自主智能体独立完成从规格定义到版图文件输出的CPU全流程设计。

Verkor自主设计的这款CPU核被命名为VerCore。它采用了五级流水线顺序执行、单发射架构。在ASAP7 7nm工艺设计套件下,VerCore能够稳定运行在1.48GHz主频,并在CoreMark基准测试中获得3261分。在性能层面,该CPU核的测试表现大致相当于Intel在2011年推出的Penryn架构赛扬SU2300移动处理器。

在设计过程中,DesignConductor系统展现了其自主优化能力,包括设计了一个主频高达2.57GHz的高速Booth-Wallace乘法器,并完成了经过多方案验证的单周期分支惩罚设计。

值得注意的是,VerCore目前仅完成了仿真环境下的功能验证,尚未进行实际的芯片流片生产。其所使用的ASAP7 7nm工艺设计套件,属于学术研究范畴,并非可用于大规模量产的商用工艺节点。

Verkor在其论文中也坦诚地指出了当前AI设计系统的局限性。AI在处理复杂设计问题时,有时可能低估其难度。此外,AI在理解硬件描述语言Verilog时可能存在偏差,并且在调试时序问题方面的效率仍有提升空间。研究团队估计,要利用该系统完成具备商业应用价值的芯片设计,仍需要5至10名行业专家的全程指导。

伴随芯片设计复杂度的不断提升,AI系统所需的计算资源也会呈现非线性增长,这构成了其大规模商业化应用的主要瓶颈。

Verkor透露,计划在4月底开源VerCore的RTL源码与构建脚本,并将在年度电子设计自动化大会上展示该芯片的FPGA实现方案。尽管此前已有AI设计CPU的相关研究成果,但Verkor的方案在实现全流程自主化方面具有独特性。

然而,目前这类AI设计芯片普遍面临着一个共性挑战:尚未有实际流片后获得的物理硅片成品出现。

GDSII(Graphic Database System II)作为全球半导体行业通用的芯片物理版图标准文件格式,是芯片设计完成并通过晶圆厂流片生产的最终“施工蓝图”。“从Spec(规格需求)到GDSII”的全流程,标志着芯片从需求定义到可量产设计的全部完成。AI能够自主输出GDSII文件,意味着它已经完成了芯片设计的全链路,而不仅仅是前端的逻辑设计,这正是Verkor.io此次成果的核心突破点所在。

Verkor.io的这项AI自主设计CPU核的探索,虽然目前仍处于早期验证阶段,但其在设计效率和流程自动化方面的尝试,无疑为未来芯片设计的演进方向提供了新的视角。它预示着AI有望在降低设计门槛、加速产品迭代方面扮演更重要的角色,但同时,也暴露了AI在理解复杂设计细节、处理潜在问题以及满足商业化需求方面仍需克服的挑战。未来,AI与人类专家的协同合作,将是推动芯片设计进入新纪元的关键。