三星DRAM技术迈入10纳米以下新纪元

三星电子突破DRAM制造瓶颈,10纳米以下级别工作晶圆成功问世

三星电子在DRAM制造技术领域实现重大突破,首次成功生产出10纳米以下的10a工艺工作晶圆。这一里程碑标志着该公司在克服DRAM技术发展中的“10纳米魔咒”方面迈出了关键一步。

根据业界消息,三星电子在上月生产了采用10a工艺的晶圆,并在随后的芯片特性检测中确认了工作晶圆的存在。这是三星电子首次在其DRAM生产中应用4F平方单元结构和垂直通道晶体管(VCT)工艺。在DRAM行业,10纳米级别的工艺通常以1x、1y、1z、1a、1b、1c、1d等代际划分,而10a工艺代表着1d之后的下一代,其电路线宽预计在9.5至9.7纳米水平,正式跨入10纳米以下的新阶段。

工作晶圆的产出,即从晶圆上切割出的芯片能够按照设计正常运作,是DRAM研发进程中的一个重要信号。这表明其设计与工艺方向是正确的,为后续的良率提升和可靠性验证奠定了基础。

三星电子的计划显示,该公司将在今年内完成基于10a工艺的DRAM开发,并在明年进行质量测试,预计于2028年正式将该技术推向量产生产线。三星计划在10a、10b、10c这三个工艺代际中持续应用4F平方和VCT结构,并有望从10d工艺开始转向3D DRAM技术。

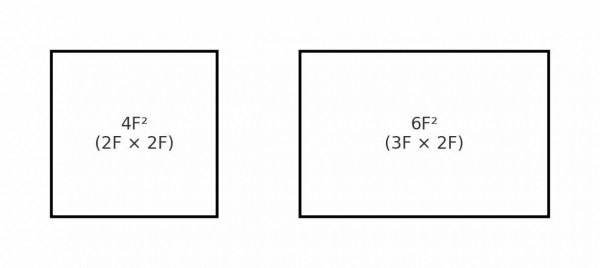

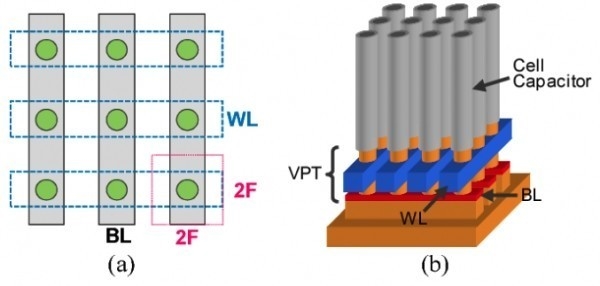

此次突破的核心在于引入了4F平方单元面积和垂直通道晶体管(VCT)这两项关键技术。相较于以往的6F平方单元面积,4F平方结构在同等芯片尺寸下能够容纳30%至50%的更多单元,这为提升DRAM的容量、速度以及降低功耗带来了显著潜力。为了在更小的单元区域内有效布局栅极、通道和电容器,三星采用了VCT技术,将电容器整合在晶体管上方,改变了传统布局模式。

随着4F平方和VCT技术的应用,核心材料的选择也随之调整。三星电子将通道材料从硅转向铟镓锌氧化物(IGZO),旨在缩小单元面积的同时有效抑制电流泄漏,并保持数据存储的稳定性。此外,围绕单元的其他外围电路将通过独立的晶圆加工,并利用晶圆对晶圆混合键合技术(W2W bonding)与PUC方案相结合进行集成。

市场分析人士指出,三星电子在此次成功产出工作晶圆后,其相关技术的开发和量产进程将得到加速。与此同时,行业内其他厂商的策略则有所差异。美光科技倾向于尽可能保持现有设计,以求稳健过渡。中国DRAM厂商由于无法获得先进的极紫外光刻(EUV)设备,在缩小线宽方面面临挑战,因此正积极布局3D DRAM,期望通过技术革新绕过光刻设备瓶颈。SK海力士则计划在10b工艺节点而非10a节点应用4F平方和VCT技术,显示出不同的技术推进节奏。

三星电子在10纳米以下DRAM制造上的突破,不仅是自身技术实力的证明,也可能引领DRAM行业进入一个更先进、更高密度的新时代,对未来存储芯片的性能和应用格局产生深远影响。